# ADM-PCIE-9V5 Support & Development Kit Release: 1.0.0

Document Revision: 1.0 27th August 2019

## © 2019 Copyright Alpha Data Parallel Systems Ltd. All rights reserved.

This publication is protected by Copyright Law, with all rights reserved. No part of this publication may be reproduced, in any shape or form, without prior written consent from Alpha Data Parallel Systems Ltd.

Head Office US Office

Addresss:

Suite LAA, 160 Dundee Street,

611 Corporate Circle, Suite H Golden, Co. 80401

Telephone:

+44 131 558 2600

(303) 954 8768

Fac:

+44 131 558 2700

(866) 820 9956 - 10l free omail:

email:

sales@alpha-ddata.com

sales@alpha-ddata.com

website:

http://www.alpha-ddata.com

http://www.alpha-ddata.com

All trademarks are the property of their respective owners.

Introduction .....

Figure 2

## Table Of Contents

| 1.1     | Structure of this package                         |     |

|---------|---------------------------------------------------|-----|

| 2       | The ADXDMA Driver                                 |     |

| 3       | Development operating system support              |     |

| 31      | Windows                                           |     |

| 3.2     | Linux                                             |     |

| 4       | Conventions used in this SDK                      |     |

| 4.1     | Version numbers                                   |     |

| 4.2     | Common HDL code                                   |     |

| 4.3     | Vivado IP repositories                            |     |

| 4.4     | Example FPGA designs                              |     |

| 5       | Associated documents                              | . 8 |

| 6.1     | Release history                                   |     |

|         | List of Tables                                    |     |

| Table 1 | Recommended Vivado version by example FPGA design | 3   |

| Table 2 | Vivado Tcl scripts used in example FPGA designs   | . 6 |

|         | List of Figures                                   |     |

|         | 0 (1.00)                                          |     |

Structure of an example FPGA design

## 1 Introduction

The ADM-PCIE-9V5 Support & Development Kit (SDK) is a set of resources for FPGA designers and software engineers working with Alpha Data's ADM-PCIE-9V5 reconfigurable computing card. The latest version of the ADM-PCIE-9V5 SDK can be found at:

https://support.alpha-data.com/Downloads.aspx?fldr\_req=Downloads/admpcie9v5/sdk

The resources of the ADM-PCIE-9V5 SDK include:

- Resources for developing application software for a machine that hosts Alpha Data reconfigurable computing hardware, using the ADXDMA Driver:

- C/C++ header files and libraries which provide Application Programming Interfaces (APIs).

- Documentation about Application Programming Interfaces (APIs).

- Utilities (with source code), which make use of the Application Programming Interfaces (APIs).

- Example FPGA designs and host programs (with source code) demonstrating various features of the ADM-PCIE-9V5:

- The DMA Demonstration FPGA Design, which demonstrates high performance DMA using the Xilinx XDMA (PCI Express) IP together with Alpha Data's ADXDMA Driver.

- Host Interface to SPI Flash Design

Demonstrates combining the Xilinx XDMA (PCI Express) IP with the Xilinx AXI SPI IP in order to create a host interface that permits the host CPU to access the on-board SPI Flash that is used to configure the FPGA.

The ADXDMA Driver includes a utility **adxdma\_spi** that allows the host CPU to erase, program and verify SPI Flash chips via the Xilinx AXI SPI IP.

- The IBERT FPGA Design, which makes use of the Xilinx IBERT IP to provide ready-to-use IBERT bitstreams that can be used to test the QSFP and OpenCAPI connectors of the ADM-PCIE-9V5.

- IP and common HDL code provided by Alpha Data:

- ADM-PCIE-9V5 Board Control Interface IP (ADM-PCIE-9V5-BCI), which provides an AXI4 Lite interface to the board's microcontroller, among other functions.

- Common HDL code (i.e. not specific to the ADM-PCIE-9V5), used by the example FPGA designs.

## 1.1 Structure of this package

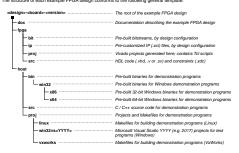

The directories making up the ADM-PCIE-9V5 SDK are organised as in Figure 1 below:

Figure 1 : Structure of the SDK

\* For more detail on the structure of the example FPGA designs, see Section 4.4.

#### 1.2 The ADXDMA Driver

The ADXDMA Driver is a kernel-mode driver for the PCI Express Endpoint in the Xilinx XDMA IP, which provides a user-mode application programming interface (API). The latest version can be found here:

https://support.alpha-data.com/Downloads.aspx?fldr\_req=Downloads/adxdma

## 2 Recommended Vivado versions

For this release of the ADM-PCIE-9V5 SDK, recommended Vivado versions for the example FPGA designs are as follows:

| Example FPGA design                     | Short name | Compatible Vivado<br>versions | Recommended<br>Vivado version |

|-----------------------------------------|------------|-------------------------------|-------------------------------|

| DMA Demonstration FPGA Design           | dma_demo   | 2017.2 - 2019.1               | 2019.1                        |

| Host Interface to SPI Flash FPGA Design | host_spi   | 2017.2 - 2019.1               | 2019.1                        |

| IBERT FPGA Design                       | ibert      | 2018.1 - 2019.1               | 2019.1                        |

Table 1 : Recommended Vivado version by example FPGA design

Please refer to the documentation for each example FPGA design for further details of any known issues that affect them.

## 3 Development operating system support

#### 3.1 Windows

Generally speaking, Alpha Data's Windows software, when supplied in binary form, is compatible with Windows XP and later. However, the choice of Windows operating system used for development mainly depends upon which releases of Microsoft Visual Studio and/or Xilinx Vivado are chosen for a project.

When developing an FPGA design, the Xilinx Vivado toolset is used and therefore a Windows operating system must be capable of running Vivado. As of writing, Vivado 2019.1 is the current release, and and as per the Vivado 2019.1 release notes §. Windows 7 SP1 and Windows 10 are recommended.

#### Vivado path length issue

In Windows, Vivado requires that path lengths of lifes are no greater than the MAX\_PATH Win32 constant, which is 260 characters (including the NUL character used to terminate a string). This limit is easily exceeded when a Vivado project uses IP (cores) and the path length of the Vivado project file (xpt) exceeds about 80 characters. Exceeding the MAX\_PATH limit can result in otherwise inexplicable failures when implementing an PFOA desirm in Vivado

The recommended workaround for this issue is to use the **subst** command to map a drive letter (e.g. **Z**:) to the root of this SDK. If done correctly, the result is the existence of directories **Z**:\text{\text{door}, **Z**:\text{\text{example}, **Z**:\text{\text{fpga}} etc.}

When developing software to run on a host machine, Microsoft Visual Studio is likely to be used for building applications. Therefore, the Windows operating system must be capable of running a particular version of Microsoft Visual Studio. For Microsoft Visual Studio 2017, Windows 7, Windows 8.1 and Windows 10 are recommended.

#### 3.2 Linux

Alpha Data generally does not supply binaries for Linux because of the large number of architectures and configurations that exist across various Linux distributions. Source code is provided, however, and can be built for most Linux distributions.

When developing an FPGA design, the Xilinx Vivado toolset is used, and therefore the supported Linux distributions depend upon the version of Vivado chosen for a project. As of writing, Vivado 2019.1 is the latest version, and as per the Vivado 2019.1 release notes \$\frac{1}{2}\$, the following Linux distributions are recommended:

- Red Hat Enterprise Workstation / Server 7.4, 7.5 & 7.6 (64-bit)

- SUSE Linux Enterprise 12.4 (64-bit)

- CentOS 7.4, 7.5 & 7.6 (64-bit)

- Ubuntu Linux 16.04.5 LTS & 18.04.1 LTS (64-bit)

Linux distributions that are not listed might result in Vivado failing to work, or only partially working. They are not supported by Xilinx.

### 4 Conventions used in this SDK

#### 4.1 Version numbers

If the name of a folder in the SDK has a suffix such as v1\_0\_0, it denotes a version number for that subtree as a whole.

#### 4.2 Common HDL code

The folder fpgaflib/ contains common HDL code used by certain example FPGA designs. Within this folder, each component (a collection of HDL source files) is a subtree whose name has a version suffix (for example, fife-v1 0 0).

### 4.3 Vivado IP repositories

The folder fpga/repo/ contains Vivado IP repositories used by certain example FPGA designs. Generally speaking, if this folder contains a sublolder XXXX.Y, it means that the IP-XACT definitions found within it are compatible with Vivado XXXX.Y or later.

The folder fpga/repo/interfaces/ might exist in some SDKs. This folder contains IP-XACT interface definitions, which are generally compatible with any version of Vivado.

#### 4.4 Example FPGA designs

The example FPGA designs, found in the example folder, consist of the following elements:

- Documentation describing the example FPGA design.

- FPGA-related:

- HDL code (VHDL / Verilog / SystemVerilog).

- · Constraints (.xdc files).

- · Tcl scripts for generating Vivado projects.

- Note that ready-made Vivado projects are not supplied; see below for an explanation of this.

- Pre-built bitstreams, generally built with the latest version of Vivado available at time of publication.

- Host-related, if required for the example FPGA design in question:

- C / C++ source and header files

- Project files for Microsoft Visual Studio and Makefiles for Linux & VxWorks, where supported for the example FPGA design in question.

- Pre-built binaries, for Windows running on Intel architecture, if supported for the example FPGA design in question.

For Linux and VXWorks, there are so many possible architectures, binary formats, compilers, environmental issues and other build options that supplying binaries is deemed impractical. For these operating systems, the user must compile demonstration programs before running them.

As mentioned above, ready-made Vivado projects are **not** supplied in this SDK, but Tcl scripts for generating Vivado projects are provided. This is for several reasons, principally:

- Vivado projects using certain IP or certain features can be broken simply by being moved within the filesystem, and such a move would always occur when the user unpacks this SDK to the folder of his or her choice.

- Vivado projects using certain IP or certain features can be broken by being upgraded (to a newer version

of Vivado). Vivado projects cannot in general be reliably downgraded (to an older version of Vivado).

- Tcl scripts for generating Vivado projects can determine the version of Vivado in use and apply

workarounds for known issues at time of publication.

The structure of each example FPGA design conforms to the following general template:

Figure 2 : Structure of an example FPGA design

Some folders may be omitted for certain example FPGA designs; for example, the IBERT FPGA Design does not have a host folder because it has no host interface and is driven solely by Vivado Hardware Manager.

#### Vivado Tcl script naming conventions

Within the fpga/proyl folder of each example FPGA design, a number of Tcl scripts are provided. Most important are the Vivado project-generation scripts, whose filenames contain the mkxpr prefix and a suffix that identifies a particular design configuration. The commonly-provided Tcl scripts are given in Table 2 below.

| General form of filename                      | Purpose                                                                                                                                                                                                                    |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| build- <design configuration="">.tcl</design> | Implements the design in Vivado for a particular design<br>configuration                                                                                                                                                   |

| debug- <design configuration="">.tcl</design> | Opens Vivado Hardware Manager and configures the FPGA in<br>a card with the bitstream for a particular design configuration.<br>These scripts can also be found in the fpga/bit/ folder of a<br>given example FPGA design. |

| flash- <design configuration="">.tcl</design> | Opens Vivado Hardware Manager and writes the bitstream (a .mcs file) for a particular design configuration into the configuration Flash memory of an FPGA card.                                                            |

| mkxpr- <design configuration="">.tcl</design> | Generates a Vivado project for a particular design configuration.                                                                                                                                                          |

Table 2 : Vivado Tcl scripts used in example FPGA designs (continued on next page)

| General form of filename | Purpose                                                                  |

|--------------------------|--------------------------------------------------------------------------|

|                          | Re-implements the design in Vivado for a particular design configuration |

#### Table 2 : Vivado Tcl scripts used in example FPGA designs

Design configurations allow for several variants to exist for a given example FPGA design. For example, in the IBERT FPGA Design, there are multiple design configurations, corresponding to different line rates and different FPGA dies (e.g. VUSP vs VUSP). In general, the total number of design configurations for a given example FPGA design is the result of enumerating the valid combinations of one or more 'orthogonal' options.

## 5 Associated documents

- (1) ADXDMA API (root)/host/adxdma-v0\_9\_8/doc/ad-ug-0105\_v1\_4.pdf

- (2) ADXDMA Board Control API (root)/host/adxdma-v0\_9\_8/doc/ad-ug-0112\_v1\_4.pdf

- (3) ADXDMA Driver Utilities

- (root)/host/adxdma-v0 9 8/doc/ad-ug-0110 v1 4.pdf

- (4) ADM-PCIE-9V5 DMA Demonstration FPGA Design (root)/example/dma\_demo-admpcie9v5-v1\_0\_0/doc/ad-ug-0131\_v1\_1.pdf

- (5) ADM-PCIE-9V5 Host Interface to SPI Flash FPGA Design (root)/example/host\_spi-admpcie9v5-v1\_0\_0/doc/ad-ug-0133\_v1\_1.pdf

- (6) ADM-PCIE-9V5 IBERT FPGA Design (root)/example/ibert-admpcie9v5-v1 0 0/doc/ad-ug-0132 v1 2.pdf

## 6 Release history

### 6.1 Release 1.0.0

This is the first release of the ADM-PCIE-9V5 Support & Development Kit.

## **Revision History**

| Date             | Revision | Nature of change                   |

|------------------|----------|------------------------------------|

| 27th August 2019 | 1.0      | Initial version for Release 1.0.0. |