Specification

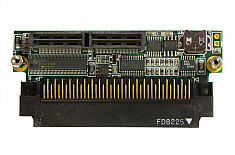

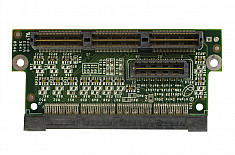

Board Format

3U VPX (OpenVPX Compliant)

Environmental Specifications

Temperature Limits | Operating Temperature Range | Storage Temperature Range |

|---|

| Min | Max | Min | Max |

|---|

| AC0 | Air Cooled Commercial | 0°C | +55°C | -40°C | +85°C |

| ACE | Air Cooled Extended | 0°C | +70°C | -55°C | +100°C |

| AC1 | Air Cooled Industrial | -40°C | +70°C | -55°C | +100°C |

| CC0 | Conduction Cooled Commercial | 0°C | +55°C | -40°C | +85°C |

| CCE | Conduction Cooled Extended | 0°C | +70°C | -55°C | +100°C |

| CC1 | Conduction Cooled Industrial | -40°C | +70°C | -55°C | +100°C |

Operating Humidity Range:

Up to 95% (non-condensing)

Host I/F

PCI Express Gen2 x1, x2 or x4 link to separate bridge device with 2GB/s local link to user FPGA

4 DMA Controllers

Interrupt Controller

Target Device

AMD Virtex® -7

XC7V585T, XC7VX330T, XC7VX485T, XC7VX690T (FF(G)1761, FH(G)1761 or FLG(G)1761)

FPGA Resources

| Chosen Device | FFs | LUTs | DSPs | BRAM |

|---|

| XC7V585T | 728k | 582k | 1260 | 28Mb |

| XC7VX330T | 408k | 326k | 1120 | 27Mb |

| XC7VX485T | 607k | 485k | 2800 | 37Mb |

| XC7VX690T | 866k | 693k | 3600 | 52Mb |

FPGA Hard IP Cores

2x PCI Express cores (Gen2 or Gen3 - FPGA dependent)

On Board Memory options

| Memory Type | No. Banks | Memory Size (per bank) |

|---|

| SDRAM | 4 | 512MB DDR3-1600 |

1GB DDR3-1600 |

Target FPGA Configuration

PCI Express direct to SelectMAP portFrom Flash direct on power upExternal JTAG connector

FPGA Configuration Flash

| Flash Type | Flash Size |

|---|

| BPI | 512MBit |

On-board Clock Specifications

Low-jitter 250MHz reference clock, suitable for SerDes applicationsLow-jitter 200MHz reference clock for IOB delay circuitsCustom clock inputs available through the XRM2 interfaceTwo Software-Programmable Clocks

I/O Interfaces

| Interface Type | Qty | Description |

|---|

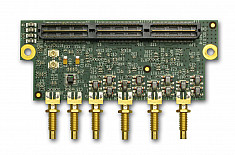

| FRONT I/O (XRM2) |

| Discrete Digital | 146 | LVCMOS/LVDS I/O (programmable to 1.2, 1.5 or 1.8V) |

High-Speed

Serial Links | 8 | High-Speed Serial Links to XRM2 |

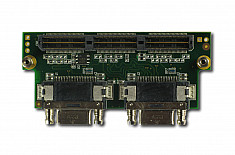

| VPX I/O (P1) |

| High-speed serial links | 1 | x4 PCI Express Interface |

| 1000Base-X Ethernet | 2 | Ethernet connectivity to VPX backplane |

| Discrete Digital | 8 | Discrete IO |

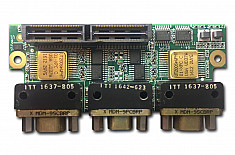

| REAR I/O (P2) |

| Discrete Digital | 64 | IO compliant with VITA 46.9 X64S |