Specification

Board Format

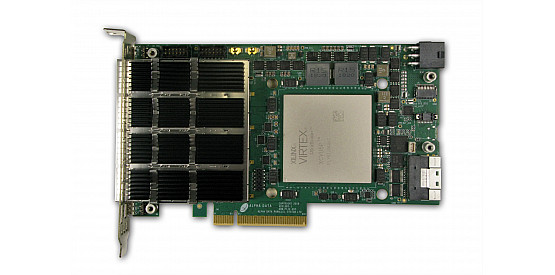

Single Slot 1/2 Length, Full Height, x8 PCIe form Factor

Width: 181.5 mm

Height: 120.9 mm

Depth: 19.7 mm

Weight: Without Fan - 590 g

Environmental Specifications

Temperature Limits | Operating Temperature Range | Storage Temperature Range |

|---|

| Min | Max | Min | Max |

|---|

| AC0 | Air Cooled Commercial | 0°C | +55°C | -40°C | +85°C |

Operating Humidity Range:

Up to 95% (non-condensing)

EMC:

See the ADM-PCIE-9V5 Declaration of Conformity document

Host I/F

PCI Express Gen3 x8 or OpenCAPI

Target Device

AMD Virtex® UltraScale Plus™

XCVU9P-3, XCVU5P-3 (FLGA2104/FLVA2104)

FPGA Resources

| Chosen Device | FFs | LUTs | DSPs | BRAM | URAM |

|---|

| XCVU9P-3 | 2364k | 1182k | 6840 | 75.9Mb | 270.0Mb |

| XCVU5P-3 | 1201k | 601k | 3474 | 36Mb | 132.2Mb |

FPGA Hard IP Cores

9x 100G Ethernet MACs (incl. KR4 RS-FEC) (6 on VU5P-3)

9x 150G Interlaken cores (6 on VU5P-3)

6x PCI Express x16 Gen3 cores (4 on VU5P-3)

Board Management

The ADM-PCIE-9V5 houses a system monitoring chip which can provide real-time temperature, voltage and current readings of the system, as well as reconfigure programmable clocks and much more. The system monitor can be accessed directly through the USB interface via the front panel (or rear of the board), the UART connection to the target FPGA or through the SMBus interface on the card's PCI Express edge connector. When enabled**, IPMI can also be used to communicate with the system monitor, allowing for remote communication and management with the ADM-PCIE-9V5.

** IPMI is disabled by default and should only be enabled when the board is installed in an IPMI-compliant system. Please contact the factory for details on enabling IPMI on the ADM-PCIE-9V5.

Target FPGA Configuration

From onboard FlashThrough USB board management (built-in JTAG)Partial Reconfiguration (via MCAP) Over PCIE

FPGA Configuration Flash

| Flash Type | Flash Size |

|---|

| QSPI | 2GBit |

High-Speed Network Interfaces

| Interface Type | Qty | Lanes per Interface | Data Rate per Lane | Protocol Capability |

|---|

| QSFP-DD | 4 | 8 | 28Gbps | User Configurable, includes 10/25/40/100G Ethernet |

| Ultraport SlimSAS | 1 | 8 | 25Gbps | OpenCAPI |

| Firefly | 1 | 4 | 28Gbps | User Configurable |